Zahlreiche industrielle Anwendungen erfordern Echtzeitdaten. Sie gewährleisten vernetzten Geräten Informationen über die Einhaltung maximaler Laufzeiten sowie Zeitinformationen mit geringem Versatz zwischen den einzelnen Knotenpunkten. Das ermöglicht eine verbesserte Synchronisierung und zeitgenaue Rückverfolgbarkeit, z.B. zwischen Produktionsabläufen und Qualitätskontrolle. Im Ergebnis führt das zu schnelleren Zykluszeiten und einer insgesamt höheren Produktivität. In der Vergangenheit wurde die Echtzeitfähigkeit durch proprietäre Systeme und Protokolle und oft über eine separate Verkabelung für zeitkritische Informationen bereitgestellt. Diese Systemarchitektur ist jedoch mit Einschränkungen der Netztopologie verbunden; alternativ muss die Datenmenge der beteiligten Geräte pro Intervall stark begrenzt werden. Außerdem limitiert die Trennung zwischen IT und OT die Skalierbarkeit und Flexibilität der Netzwerke und vervielfacht den Aufwand für Verkabelung und Wartung.

Ein Netzwerk für alle Daten

TSN überwindet diese Einschränkungen. Alle Informationen sind im selben IoT-Netzwerk und für alle angeschlossenen Geräte sichtbar. Der Verkabelungsaufwand kann drastisch reduziert werden, weil nur noch ein gemeinsames Kabel für alle Übertragungsprotokolle zum Einsatz kommt. Time-Sensitive Networking nutzt dafür virtuelle LANs in der Ethernet-Infrastruktur und ermöglicht so Determinismus für ausgewählte Datenströme. Verschiedene Datentypen können damit in einem gemeinsamen Netzwerk übertragen werden, ohne gegenseitig Echtzeit-Eigenschaften zu beeinträchtigen. Das macht TSN zu einer passenden Lösung, wenn Daten mit hoher Bandbreite – z.B. Videodaten – parallel zu zyklischen Steuerungen, Management-, Diagnose- und Überwachungsanwendungen oder gleichzeitig zu Peer-to-Peer-Datenverkehr wie z.B. beim Software-Download verarbeitet werden müssen.

Verkürzt Entwicklungszeiten

Um alle Vorteile der Technologie nutzen zu können, bedarf es Ethernet-Frontend-Geräten mit nativen TSN-Fähigkeiten. Um deren schnelle und einfache Entwicklung zu ermöglichen, haben AMD, Hema und SoC-e ihr Knowhow in einem TSN-over-Ethernet-Paket gebündelt. Es basiert auf der Embedded-Vision-Plattform von Hema Electronic, mit AMD Kria System-on-Module und einem dedizierten TSN-IP-Core von SoC-e. Mit der modularen Plattform können Kunden individuelle Mainboards nach ihren Anforderungen spezifizieren. In nur wenigen Wochen erhalten Anwender einen ersten seriennahen Prototyp ihrer Hardware, der eine schnelle und einfache Entwicklung der Softwareanwendung und eine schnelle Serienqualifizierung ermöglicht.

Modulare Plattform für TSN-Elektroniken

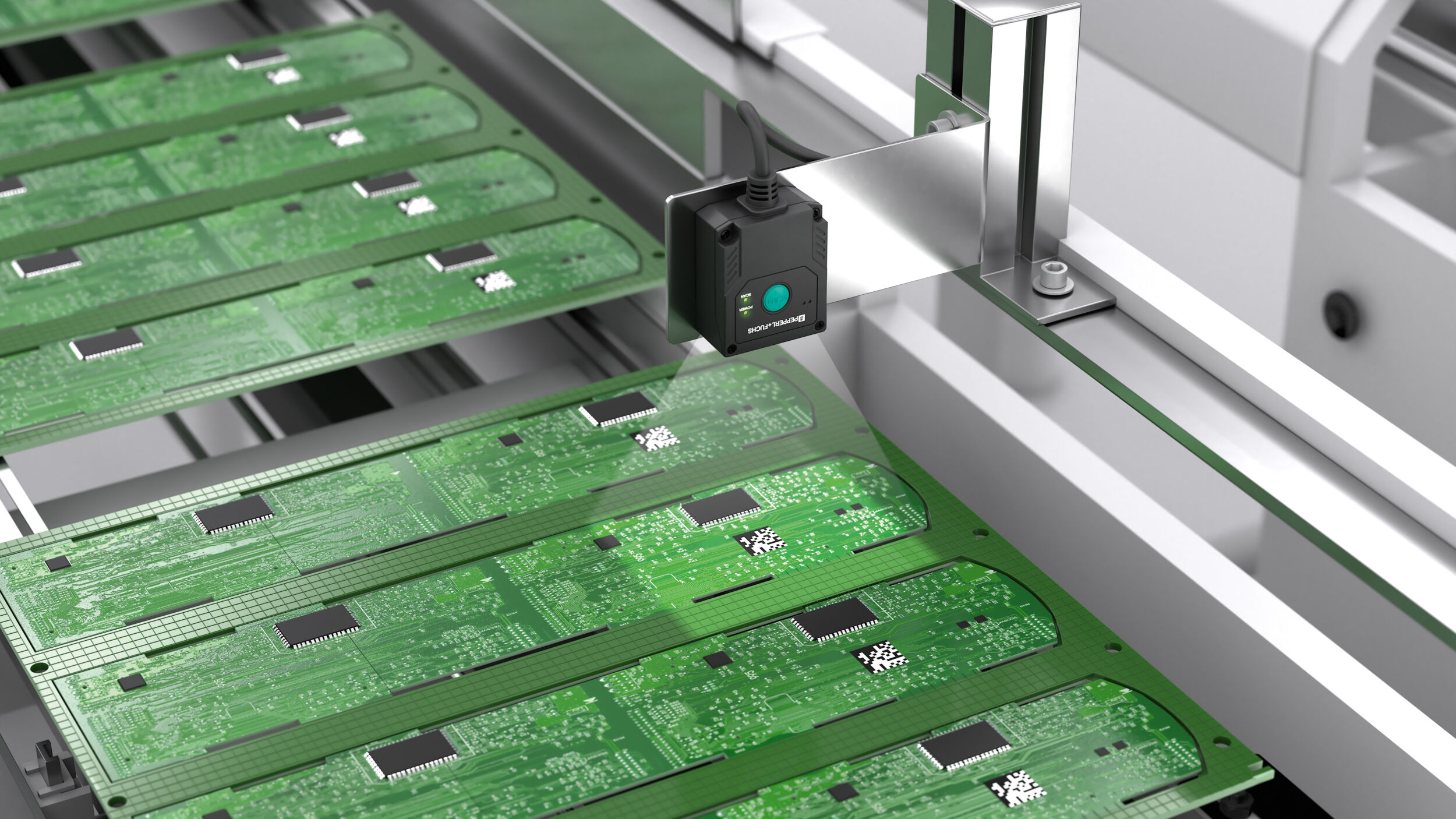

Das Kria SOM liefert die Rechenleistung für die Plattform und besteht aus programmierbaren FPGA SoCs sowie ARM Cortex-A53- und R5F-Rechenkernen. Der Vorteil dieses heterogenen Designs: Die FPGAs können zum einen die exakte Steuerung des Ausgangsverkehrs übernehmen, inklusive taktgenauer Steuerung des Auslesens der Puffer für abgehenden Verkehr; außerdem entlasten sie die weiteren Prozessoren, in dem sie die sich wiederholenden Aufgaben des Data Link Layers übernehmen. Die ARM-Cores sind frei programmierbar und können anwendungsspezifische Software ausführen, mit perfektem Zugriff auf die zuvor TSN-verarbeiteten Daten aus dem FPGA. Die Kria SoMs wurden für KI-Unterstützung entwickelt und ermöglichen die Nutzung rechenintensiver Technologien wie Machine Vision und Vision AI.